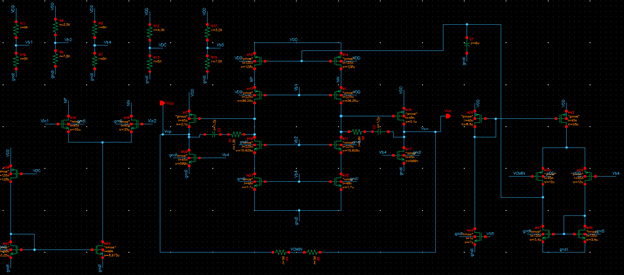

As part of an analog circuit design course, I designed an OTA amplifier in 45nm technology. The architecture was a two-stage design with a folded-cascode at the input and a common-source in the second stage. The design utilizes Miller compensation and CMFB to ensure proper bias and stability. The design uses a 1V supply, and achieves 560 MHZ Unity-Gain BW. The design consumes 1.6mW of DC power including biasing.