With the emergence of the field of Brain-Machine

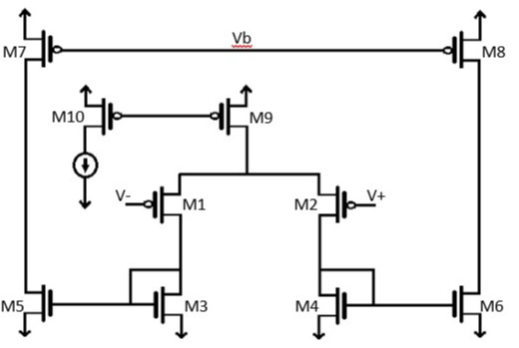

Interfaces (BMI), a question of portability and high performance immediately arises. Neural signals are characterized to be of low-amplitude and low-frequency. This requires a meticulous effort to be implemented designing the analog front-end (AFE). In this project, we demonstrate the design of a low-power, low-noise neural amplifier with an adjustable variable gain. The first stage is composed of a Low-Noise Amplifier (LNA) followed by a Programmable-Gain Amplifier (PGA). Our simulations show a working eight-channel neural amplifier in CMOS 90-nm process operating with a 1V supply, achieving an input-referred noise of less than 10uVrms while consuming less than 3.125uW/channel. I was responsible for the LNA Design.