Abstract

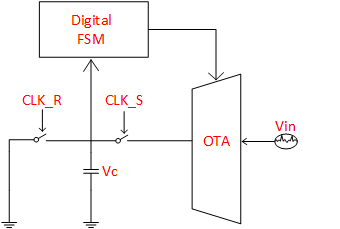

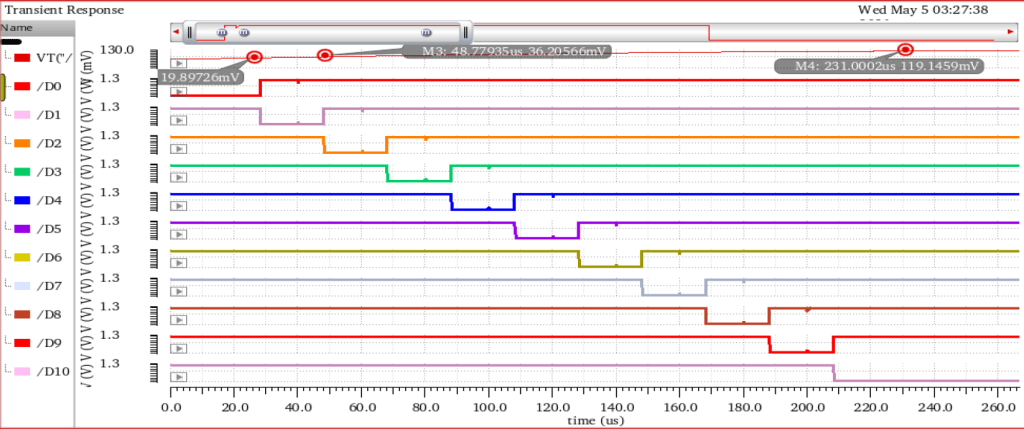

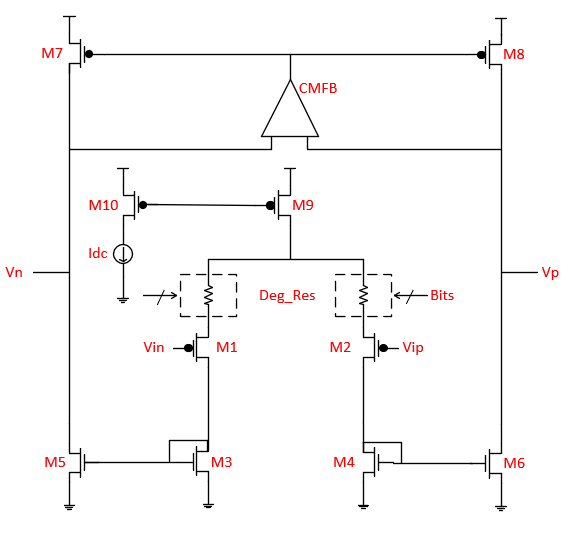

With the emergence of the field of Brain-Machine Interfaces (BMI), a question of portability and high performance immediately arises. Neural signals are characterized to be of low-amplitude and low-frequency. This requires a meticulous effort to be implemented designing the analog front-end (AFE). Neural AFEs suffer from Stimulation Artifacts (SA) that deem the circuit blind to any brain activity during stimulation. We demonstrate the design of a low-power, low-noise neural amplifier utilizing a novel approach in SA sensing, re-programming the amplifier to tolerate SA up to 100mV while sensing Local Field Potentials (LFPs) using degeneration and voltage-to-time conversion. The simulations show a working neural amplifier in CMOS 180-nm process operating with a 1.2V supply while consuming less than 7μW of power.